Сторінка 1 з 3

SI 5351

Додано: П'ят лютого 10, 2023 7:13 pm

Freddy

Намагаюся зрозуміти як керувати сішкою. Прочитав апноут AN619 і даташит на цю мікруху. Мій іншліш не дуже тому зрозуміло не все . Питання як вирахувати a.b.c i x.y.z . Точніше x.y. Наскільки відомо A це множник фапч а X це дільник мультисинтезу ,відповідно b.c та y.z це дробна частина . Алгоритм розрахунку я знайшов але отримані параметри не співпадають з результатами які я отримав в clock builder. Хто що може підказати по цій темі . Алгоритм додаю .

if(Fclk < 81000000) {

// Valid for Fclk in 0.5..112.5 Meg range

// However an error is > 6 Hz above 81 Megs

a = 36; // PLL runs @ 900 Meg

b = 0;

c = 1;

int32_t Fpll = 900000000;

x = Fpll/Fclk;

t = (Fclk >> 20) + 1;

y = (Fpll % Fclk) / t;

z = Fclk / t;

Re: SI 5351

Додано: П'ят лютого 10, 2023 8:01 pm

oldPsyho

Freddy писав: ↑П'ят лютого 10, 2023 7:13 pm

Намагаюся зрозуміти як керувати сішкою. Прочитав апноут AN619 і даташит на цю мікруху. Мій іншліш не дуже тому зрозуміло не все . Питання як вирахувати a.b.c i x.y.z . Точніше x.y. Наскільки відомо A це множник фапч а X це дільник мультисинтезу ,відповідно b.c та y.z це дробна частина . Алгоритм розрахунку я знайшов але отримані параметри не співпадають з результатами які я отримав в clock builder. Хто що може підказати по цій темі . Алгоритм додаю .

if(Fclk < 81000000) {

// Valid for Fclk in 0.5..112.5 Meg range

// However an error is > 6 Hz above 81 Megs

a = 36; // PLL runs @ 900 Meg

b = 0;

c = 1;

int32_t Fpll = 900000000;

x = Fpll/Fclk;

t = (Fclk >> 20) + 1;

y = (Fpll % Fclk) / t;

z = Fclk / t;

Дивись тут

Si5351

Re: SI 5351

Додано: П'ят лютого 10, 2023 11:13 pm

Freddy

я цю бібліотеку курю вже декілька днів але до кінця не можу розібратися .

ref_freq = xtal_freq[(uint8_t)plla_ref_osc] *SI5351_FREQ_MULT де SI5351_FREQ_MULT це множник фапч чи ділитель мультисинтезу ? далі if (freq < SI5351_PLL_VCO_MIN * SI5351_FREQ_MULT) { freq = SI5351_PLL_VCO_MIN * SI5351_FREQ_MULT; }SI5351_PLL_VCO_MIN це походу мінімаотна частота фапч яка дорівнює 600 mHz.

Re: SI 5351

Додано: Суб лютого 11, 2023 5:35 pm

UR5FFR

Алгоритм буде працювати але він зовсім геть поганий - буде давати дуже великий джиттер та фазовий шум.

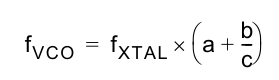

5351 має VCO який працює у діапазоні 600-900МГц. Частота VCO задається через PLL та дорівнює

- si5351_01.png (4.73 Кіб) Переглянуто 66314 разів

Важливо розуміти, шо числа

a,

b та

c - цілі. Крім цього значення

a повинно буди у діапазоні від 15 до 90. А

b та

c - від 0 до 0xFFFFF - тобто вони займають 20 біт. Вихідна частота отримується діленням частоти VCO

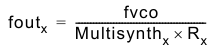

- si5351_02.png (3.8 Кіб) Переглянуто 66314 разів

Коефіцієнт ділення multisynth теж може бути дробовим та має ту ж саму формулу що й для PLL. Також є додатковий коефіцієнт ділення R для отримання низьких частот, коли діапазону коефіцієнта multisynth не вистачає.

З точки зору отримання найменших фазових шумів потрібно щоб multisynth не застосовував дробових коефіцієнтів. Він повинен ділити частоту VCO націло. Також треба щоб він був парний (молодший біт дорівнює нулю).

Алгоритм для отримання частоти F має десь такий вигляд:

1. Обираємо частоту VCO. Чим вище - тім краще. Але попадаються глючні китайські сішки де VCO вище 800МГц не працює. Тому ставимо посередині Fvco = (900+600)/2 = 750МГц

2. Розраховуємо цілий multisynth коефіцієнт ділення. x = int(Fvco/F). y=0, z=0xFFFFF

3. Уточнюємо частоту VCO: Fvco = F*x

4. Розраховуємо коефіцієнти для PLL:

a = int(Fvco/Fxtal)

b = (Fvco-Fxtal*a)*0xFFFFF/Fxtal

c = 0xFFFFF

Усюди int - це ціла частина числа.

Частота на виході може мати невеличку похибку десь кілька Гц.

Cclock builder працює інакше - йому до біса фазові шуми, тому він робить дрібний multisynth. Частота буде на виході без помилки.

Ось посилання на мій репо з бібліотекою

https://github.com/andrey-belokon/UR5FFR_Si5351 - вивчайте

Re: SI 5351

Додано: Суб лютого 11, 2023 7:33 pm

Freddy

це я зрозумів з мануала . я знаю що для модуля на si5351 де стоїть кварц на 25 мгц діапазон множника фапч буде 24-36. для частот 1.5-30 мгц доцільно використати 36 (а=36 ,b= 0,y=1) при цьому pll буде 900 мгц а далі 900 мгц ділимо . Для частоти 3.1мгц в мене вийшло x =290 (p1=36649), y=333333(p2=299971),z=103333(dp3=10533333) . X,Y,Z рахував по цьому алгоритму

int32_t Fpll = 900000000;

x = Fpll/Fclk;

t = (Fclk >> 20) + 1;

y = (Fpll % Fclk) / t;

z = Fclk / t;

clock builder report для цієї самої частоти додаю

Inputs:

IN0: 25 MHz

Outputs:

OUT0: 3.1 MHz

Enabled LVCMOS 8 mA

Offset 0.000 s

OUT1: Unused

OUT2: Unused

Frequency Plan

==============

PLL_A:

Enabled Features = None

Fvco = 899.775 MHz

M = 35.991

Input0:

Source = Crystal

Source Frequency = 25 MHz

Fpfd = 25 MHz

Load Capacitance = Not_Applicable

Output0:

Features = None

Disabled State = StopLow

R = 1 (2^0)

Fout = 3.1 MHz

N = 290.25

0x001C[17:0] MSNA_P1 4094 0x00FFE

0x001F[19:0] MSNA_P2 848 0x00350

0x001F[23:4] MSNA_P3 1000 0x003E8

0x002C[17:0] MS0_P1 36640 0x08F20

0x002F[19:0] MS0_P2 0 0x00000

0x002F[23:4] MS0_P4 4 0x00004

Re: SI 5351

Додано: Суб лютого 11, 2023 7:39 pm

Freddy

якщо зрозумів правильно то , multisynth divider є парне число а за допомогою множника N B PLL точно підганяєм вихідну частоту ?

Re: SI 5351

Додано: Нед лютого 12, 2023 11:22 am

UR5FFR

Я не знаю як працює clock builder і ніколи цим не цікавився. Я навів вам алгоритм та основні принципи роботи моєї бібліотеки. Множник PLL треба робити дрібним. А multisynth divider - цілим та парним. При зміні частоти на невелику дельту змінюємо множник PLL. При суттєвій зміні частоти - змінюємо multisynth divider та робимо ресет PLL - це викликає невелике клацання

Re: SI 5351

Додано: Нед лютого 12, 2023 6:23 pm

Freddy

в планах зробити свій простий синтез для простих конструкцій. я думав просто вираховувати множники в залежності від бажаного виходу . там діапазон частот буде невеликий тому міняти multisynth не планую а там побачимо . хочу зрозуміти як це працює і випробувати . як дійде до лабораторки там побачу . Покищо ціль змусити сішку генерувати те що я хочу і зрозуміти як рахувати pll та multisynth .

Re: SI 5351

Додано: Нед лютого 12, 2023 8:22 pm

UR5FFR

Воно похвально що ви намагаєтеся розібратися у нутрощах. Але повірте мені - робота з 5351 - це лише кілька процентів коду сінтезатора

Свого часу я писав цю бібліотеку тому що в мене були свої вимоги і я не знайшов нічого що б працювало як мені потрібно. Тобто це був вимушений крок

Re: SI 5351

Додано: Вів лютого 21, 2023 10:25 pm

Freddy

Адреса SI5351 по замовчуванню 0x60 ? Вона завжди така чи є варіанти змінити ? В мануалі цієї інфи не знайшов (або не побачив )